STM32 IWDG Independent Watchdog Timer (IWDG ) là một loại Timer rất hay được sử dụng trong thực tế, chức năng chủ yếu của Timer này là kiểm tra vi điều khiển có bị treo hay hoạt động sai không. Từ đó đưa ra lệnh Reset, khiến chương trình chạy lại từ đầu.

Bài 14 trong serie Học lập trình STM32 từ A tới Z

Watchdog Timer là gì?

Watchdog dịch ra nghĩa là Nhìn Chó ….. Đùa đấy =)), Theo Google dịch Watchdog là người canh gác, bảo vệ việc các tác nhân bên trong hoặc bên ngoài không mong muốn làm ảnh hưởng tới sự hoạt động của vi điều khiển.

Bảo vệ của MCU

STM32 IWDG trong vi điều khiển STM32

Watchdog Timer là bộ ngoại vi tích hợp trên vi điều khiển STM32 có khả năng giúp cho người dùng phát hiện ra hệ thống bị treo, chạy sai và tạo ra một ngắt hoặc một tín hiệu reset chip.

Đối với các sản phẩm điện tử được phát hành ra ngoài thị trường, thì do nhiều yếu tố bên trong (code chưa chặt chẽ, code có bug…) và yếu tố bên ngoài (nhiễu, điều kiện nhiệt độ, độ ẩm) dẫn đến việc hoạt động sai của VDK dẫn đến các hiện tượng chạy chức năng bị sai, hoặc treo chip. Trong trường hợp như vậy chúng ta cần có các biện pháp khắc phục tạm thời ví dụ như reset chip để chạy lại chương trình. Thì bộ Watchdog Timer được sinh ra với mục đích tạo ra một tín hiệu reset bằng Software (điều khiển ngắt bằng phần mềm).

Trong STM32 Watchdog Timer có 2 loại đó là:

- Independent Watchdog Timer hay STM32 IWDG

- Window Watchdog Timer hay STM32 WWDG

Sự khác nhau giữa IWDG và WWDG

IWDG và WWDGđược tạo ra chung một mục đích thế nhưng chúng có sự khác nhau một chút về cách hoạt động và mục đích hoạt động.

Independent Watchdog Timer

Đúng như cái tên Independent chính là độc lập, nghĩa là bộ Timer này sử dụng nguồn xung LSI (Low-speed clock) vì vậy chúng có thể hoạt động ngay cả khi nguồn clock của chương trình chính không hoạt động. Điều này phù hợp với chức năng kiểm soát lỗi treo chip kể cả do phần cứng hoặc phần mềm. Khi ngắt IWDG sảy ra, MCU sẽ lập tức bị reset mà không cần làm gì cả.

Có thể tưởng tượng IWDG là một người bảo vệ của tòa nhà, trong tòa nhà đó có 1 công ty là MCU của các bạn. Vì bảo vệ đó không phải nhân viên của Công Ty MCU vậy nên cho dù MCU có hoạt động hay không hoạt động, gã bảo vệ đó vẫn sẽ thực hiện công việc của mình.

Window Watchdog Timer

Với WWDG chúng có nguồn xung từ bộ APB1 Clock nghĩa là bộ Timer này sẽ hoạt động khi chương trình hoạt động. Một khi sảy ra treo hệ thống liên quan tới Clock chính. Bộ Timer này sẽ không hoạt động.

Vậy nên chức năng chính của WWDGlà kiểm xoát lỗi phần mềm (các Bug), nếu các tác vụ (Task) hoạt động bất thường như kết thúc sớm hơn hoặc muộn hơn dự kiến, ngắt WWDG sẽ sảy ra, ngắt WWDG cho phép chương trình thực thi một số lệnh trong ngắt trước khi Reset hoàn toàn MCU.

Có thể tưởng tượng WWDG chính là một người quản lý của công ty. Người này có chức năng kiểm xoát sự hoạt động của nhân viên, ghi lại các lỗi nếu thấy nhân viên hoạt động sai. Từ đó tìm ra lỗi, các phần tử không đạt yêu cầu. Tất nhiên, nếu toàn bộ công ty đó không hoạt động, bộ WWDG này cũng không hoạt động.

Independent Watchdog Timer trong STM32

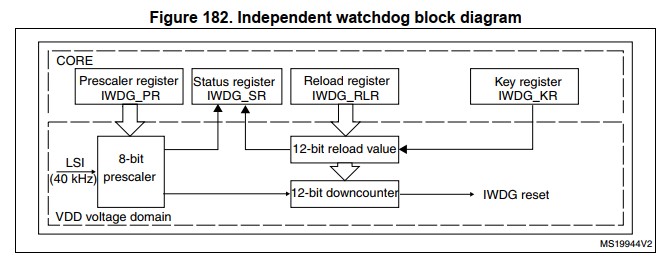

Sơ đồ khối của bộ STM32 IWDG

Ba gồm:

- IWDG_PR: Thanh ghi hệ số chia, thanh ghi này sẽ xác định thời gian mỗi 1 lần giảm của counter

- IWDG_SR: Thanh ghi trạng thái lưu trạng thái prescaler update và reload update khi có sự khiện ghi vào 2 thanh ghi này

- IWDG_RLR: Thanh ghi lưu giá trị nạp lại để nào vào bộ 12-bit reaload counter

- IWDG_KR: Thanh ghi điều khiển việc chạy và nạp lại cho bộ IWDG

Nguyên lý hoạt động của STM32 IWDG

- IWDG_PR và IWDG_RLR được nạp vào xác định chu kì tràn của downcounter

- Khi nạp vào thanh ghi IWDG_KR giá trị 0xCCCC timer sẽ bắt đầu hoạt động

- Trước khi downcounter đếm từ giá trị nạp lại tới 0 nếu ghi vào IWDG_KR giá trị 0xAAAA thì bộ counter sẽ đếm lại từ đầu (giá trị reload)

- Nếu downcounter đếm đến 0, một sự kiện reset sẽ được sinh ra và reset chip

Vậy nên để chip không bị reset chúng ta cần nạp 0xAAAA vào IWDG_KR trước khi counter đếm đến 0.

Các tham số cần quan tâm

Khi khởi tạo Timer trước khi ghi vào 2 thanh ghi PR và RLR cần ghi vào KEY giá trị 0x5555 để bỏ chế độ bảo vệ của timer.

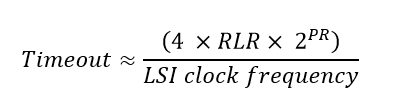

Chu kì đếm của Timer xác định bởi hệ số chia và giá trị thanh ghi Reload, theo công thức.

Trong chế độ Debug để chip không reset liên tục ta cần enable bit DBG_IWDG_STOP để tắt timer này đi.

Lập trình STM32 IWDG

Kịch bản đặt ra: Trong chương trình chính ta sẽ đảo trạng thái led PCB13 liên tục, sau mỗi lần đảo trạng thái chúng ta sẽ làm mới timer, vậy nên MCU sẽ không reset.

Khi nhấn nút tại PA0, chương trình chính sẽ đi vào while(1) và không làm mới timer, vậy nên led sẽ đứng yên tại thời điểm nhấn nút sau mấy giây rồi bắt đầu lại nháy như thường

Cấu hình STM32 IWDG trên CubeMX

Mở CubeMX chọn chip, trong SYS chon debug wire

Trong tab IWDG chọn Active và set thông số như hình. Ta sẽ có chu kì tràn của Timer là 2s

Trong tab GPIO chọn PC13 là GPIO_OUT đặt tên là Led, PA0 là GPIO_IN đặt là Button

Gen code và mở trong keilc

Lập trình STM32 IWDG trên KeilC

Trước while(1) chúng ta khởi tạo bộ IWDG, trong while đảo trạng thái led mỗi 0,5s, sau đó làm mới timer.

Khi nút nhấn PA0 được bấm, chương trình sẽ rơi vào vòng lặp vô hạn. Khi vào while 1 đủ 2s, MCU sẽ tự reset và bắt đầu nháy lại từ đầu

KẾT

STM32 IWDG là 1 Timer được sử dụng khá phổ biến, chúng sẽ rất hữu dụng khi đối phó với các tác nhân không thể kiểm xoát được từ bên ngoài làm hệ thống hoạt động sai.

Chúc các bạn học tập thật tốt, và nhớ đánh giá bài viết này nếu thấy hay nhé !!!