Thiết kế bộ lọc thông thấp : Vài năm trước, một giảng viên của tại Khoa học Địa chất đã đề nghị tôi thiết kế và chế tạo một bộ cảm biến địa từ. Các cảm biến được sử dụng để đo sự dao động trong từ trường cục bộ của Trái đất gây ra bởi nhiễu động khí tượng ở xa, đặc biệt là nhiễu loạn do sét ở xa.

Thông tin về độ dẫn điện cục bộ của vỏ Trái đất có thể được lấy từ dữ liệu này và được sử dụng để tìm một số loại mỏ khoáng sản (những mỏ có độ dẫn điện đặc biệt cao hoặc thấp – nước, quặng và dầu) và để giải thích cấu trúc của lớp vỏ. Hầu hết các dữ liệu nằm gần tần số cộng hưởng của các lỗ được hình thành bởi tầng điện ly và bề mặt của lõi Trái đất. Các tần số này nằm trong khoảng 7 Hz trở xuống, với một số thông tin lên đến khoảng 20 Hz.

Các cảm biến là những cuộn dây đơn giản với lõi hình que dài bằng sắt biến áp nhiều lớp. Các hệ thống này gặp vấn đề nghiêm trọng với nhiễu từ trường của đường dây điện 60 Hz và sóng hài của chúng, bất kể phép đo được thực hiện ở đâu. Về cơ bản, không có nơi nào trên Trái đất, thậm chí là sa mạc hoang vu, hoàn toàn không có trường từ việc phân phối năng lượng điện.

Hệ thống đã sử dụng các bộ lọc để loại bỏ nhiễu ngoài dải, đặc biệt là nhiễu ở tần số 60 và 120 Hz. Các bộ lọc cần thiết để có một số khuếch đại khiêm tốn để giúp đưa các mức tín hiệu cảm biến lên đến điện áp có thể sử dụng mà không gây ra các vấn đề về nhiễu hoặc dải động. Hãy xem xét thiết kế của một bộ lọc thông thấp cho một ứng dụng như vậy với mức cắt ở 20 Hz và độ lợi DC là 20 DB. Để đáp ứng yêu cầu triệt tiêu tần số 60 Hz, chúng tôi yêu cầu độ lợi của nó ở 60 Hz phải nhỏ hơn ít nhất 35 Db so với ở DC.

Vì các cảm biến có trở kháng nguồn khoảng 2K, nên chúng tôi yêu cầu bộ lọc phải có trở kháng đầu vào ít nhất 10 K ohms. Để thuận tiện, chúng tôi sẽ giả định rằng một bộ lọc Butterworth sẽ phù hợp. (Đầu ra của cảm biến chuyển đến bộ chuyển đổi ADC, vì vậy cần có sự thỏa hiệp giữa mức cắt và độ tuyến tính của pha. Bộ lọc Butterworth là phương pháp phổ biến vào thời điểm đó để đáp ứng sự cân bằng này. Hệ thống cũng sử dụng bộ lọc cấm dải ở 60 và 120 Hz để loại bỏ nhiều điện nhiễu dòng.)

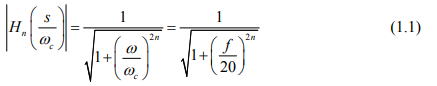

Điều đầu tiên chúng ta cần biết là bộ lọc Butterworth sẽ phù hợp với đặc điểm kỹ thuật loại bỏ tần số 60 Hz. Độ lớn của hàm truyền đối với bộ lọc ơt tần số cắt 20 Hz bậc n là:

35 Db là tỷ lệ 56,2: 1 nên : |H(f=60)≤0.018|

và ![]()

Bậc n có thể được xác định là số nguyên đầu tiên lớn hơn nghiệm của phương trình này. Dễ dàng kiểm tra rằng n = 4 thỏa mãn yêu cầu.

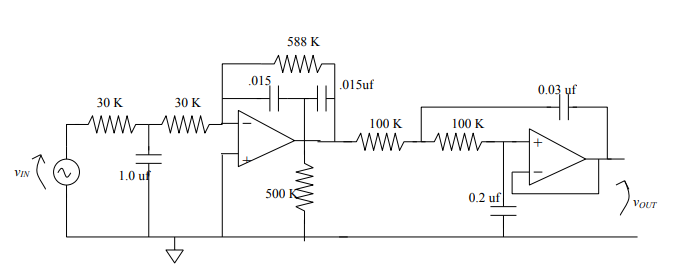

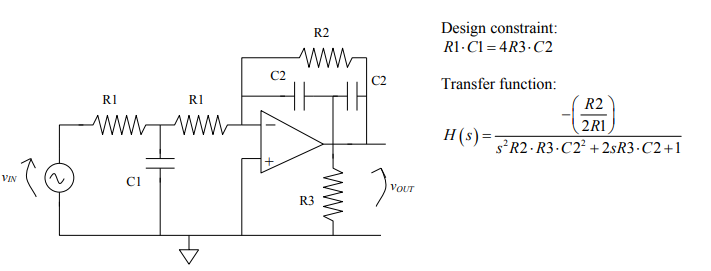

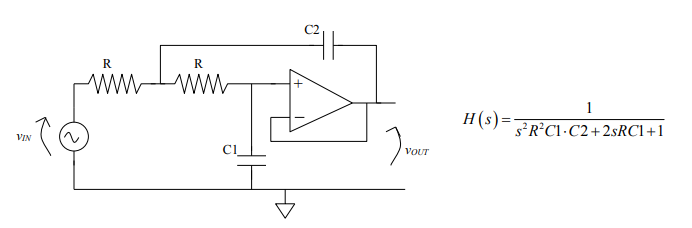

Vì bộ lọc bậc 4 là bắt buộc nên nó có thể được tạo từ hai phần bậc hai. Đối với giai đoạn đầu tiên, chúng tôi sẽ sử dụng mạch được hiển thị trong Hình 1, cũng đưa ra các phương trình thiết kế chính. Tất cả hệ thống khuếch đại sẽ được đưa vào giai đoạn này để có hiệu suất tiếng ồn tốt nhất. Dạng nhân tử của hàm lọc Butterworth bậc 4 với ngưỡng cắt 1 rad / s là:

![]()

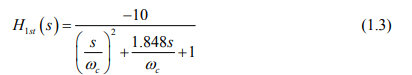

Chúng tôi sẽ gán hệ số đầu tiên cho giai đoạn đầu tiên vì nó có yêu cầu Q thấp nhất. Chia tỷ lệ yếu tố đó cho tần số và độ lợi ngụ ý rằng hàm truyền của giai đoạn đầu tiên phải là:

Trong đó : ![]()

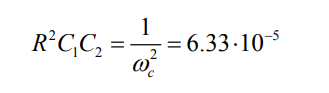

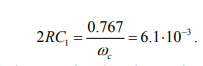

Bằng cách so sánh với các phương trình thiết kế của Hình 1, chúng ta có các phương trình sau cho các giá trị thành phần:

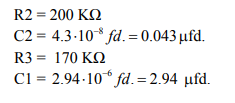

Đây là bốn phương trình trong năm ẩn số, đó là R1, R2, R3, C1 và C2. Một giá trị thành phần có thể tự do lựa chọn tùy ý trong giới hạn đáp ứng yêu cầu rằng z in ít nhất là 10 K ohms. Đối với tần số tín hiệu gần DC z in = 2 .R1, trong khi ở tần số trên 20 Hz, trở kháng sẽ gần bằng z in = R1. Vì vậy, chúng tôi sẽ chọn R1 = 10 K ohms, lưu ý rằng sự lựa chọn có thể được sửa đổi tăng lên nếu các tụ điện có giá trị lớn . Với sự lựa chọn R1 này, các nghiệm của phương trình trong dãy tìm được chúng là:

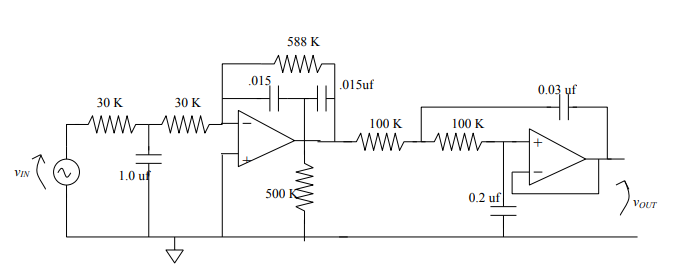

Hình 2 cho thấy một bộ lọc Sallen Key với độ lợi hợp nhất mà chúng ta sẽ sử dụng cho giai đoạn thứ hai. Chia tỷ lệ của hệ số bậc hai thứ hai trong hàm lọc Butterworth cho tần số cắt 20 Hz và so sánh nó với hàm truyền trong Hình 2 dẫn đến các phương trình thành phần:

và

Một lần nữa, có một phương trình thiết kế ít hơn số thành phần chưa biết. Điều này nói chung là đúng trong các mạch opamp vì hiệu suất của một mạch có bộ khuếch đại hoạt động lý tưởng chỉ phụ thuộc vào tỷ lệ của các giá trị thành phần hơn là giá trị tuyệt đối của chúng. Nếu người ta chọn R = 10 Kohm thì các tụ điện là C1 = 0,305 μfd và C2 = 2,08 μfd.

Trong khi điều này hoàn thành một thiết kế, vẫn còn một số chi tiết thực tế cần xem xét. Tất cả các tụ điện cần phải có dung sai tốt. Chúng không thể là tụ điện vì điện áp trên chúng có thể là cả dương và âm. Các tụ điện chính xác, không phân cực có xu hướng đắt tiền và lớn hơn. Hơn nữa, chúng ta sẽ cần sử dụng các giá trị tiêu chuẩn, và tụ điện không có sẵn nhiều giá trị như điện trở. Giá trị tiêu chuẩn lớn nhất mà tôi cảm thấy có thể chấp nhận được là 1 μfd. Do đó, tôi sẽ mở rộng quy mô tất cả các điện trở trong giai đoạn đầu tiên bằng hệ số ba và tất cả các tụ điện giảm xuống bằng hệ số 2,94. (Điều đó làm thay đổi mức cắt lên theo hệ số 3 / 2,94 = 1,02. Vì dung sai của tụ điện là 5% nên sai số này không đáng kể.) Điều này làm cho hai giá trị tụ điện là 1 μfd và 0,015 μfd, cả hai đều là giá trị tiêu chuẩn. Các điện trở 30 K cũng là tiêu chuẩn và các giá trị 500 K và 588 K có sẵn trong dung sai 1%. Tương tự, giai đoạn thứ hai phải được thu nhỏ và các tụ điện của nó được làm tròn thành các giá trị tiêu chuẩn. Tôi đã mở rộng giai đoạn đầu tiên bằng một hệ số tối thiểu để dòng điện phân cực đầu vào của nó sẽ không trở thành yếu tố được xem xét trong độ ổn định bù. Đây không phải là sự cân nhắc trong giai đoạn thứ hai vì lợi ích trong giai đoạn đầu tiên. Đối với giai đoạn sau, hệ số tỷ lệ lớn hơn 10 là hợp lý. Các tụ điện trở nên 0,2 μfd và 0,03 μfd. Hệ thống cuối cùng được hiển thị trong Hình 3 với tất cả các giá trị được chia tỷ lệ. Khi kiểm tra lần cuối, người ta có thể muốn sử dụng SPICE để xác nhận rằng ảnh hưởng của dung sai thành phần và bandwidth bộ khuếch đại thuật toán sẽ vẫn luôn để lại hệ thống với đáp tuyến tần số chấp nhận được.

Hình 1 : Bộ lọc thông thấp bậc 2 với độ lợi.

Hình 2 : Bộ lọc Sallen-Key và hàm truyền của nó.

Hình 3 : Thiết kế bộ lọc thông thấp cuối cùng.