Trong phần hướng dẫn trước, chúng ta đã xem xét Cổng NOT được gọi là Cổng đảo và chúng ta thấy rằng trạng thái đầu ra của cổng NOT là phần bù, đối nghịch hoặc nghịch đảo của tín hiệu đầu vào của nó.

Vì vậy, ví dụ, khi đầu vào duy nhất cho cổng NOT là “CAO”, trạng thái đầu ra của nó sẽ KHÔNG là “CAO”. Khi tín hiệu đầu vào của nó là “THẤP” thì trạng thái đầu ra của nó sẽ KHÔNG là “THẤP”, hay nói cách khác là nó “đảo ” tín hiệu đầu vào của nó, do đó có tên là “Cổng đảo”.

Nhưng đôi khi trong các mạch điện tử kỹ thuật số, chúng ta cần phải cách ly các cổng logic với nhau hoặc để chúng truyền động hoặc chuyển mạch cao hơn tải bình thường, chẳng hạn như rơle, solenoid và đèn mà không cần đảo. Một loại cổng logic đầu vào duy nhất cho phép chúng ta làm điều đó được gọi là Cổng đệm buffer .

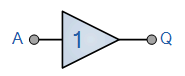

Không giống như đầu vào đơn, cổng đảo đầu ra đơn hoặc cổng NOT như TTL 7404 đảo hoặc bổ sung tín hiệu đầu vào của nó trên đầu ra, “Bộ đệm” không thực hiện khả năng đảo hoặc ra quyết định (như cổng logic có hai đầu vào trở lên) mà thay vào đó tạo ra đầu ra khớp chính xác với đầu vào của nó. Nói cách khác, cổng đệm không làm gì cả khi trạng thái đầu ra của nó bằng trạng thái đầu vào của nó.

Khi đó các Cổng đệm buffer có thể được coi là các cổng Idempotent áp dụng Luật Idempotent của Boole vì khi một đầu vào đi qua vùng nhớ này thì giá trị của nó không bị thay đổi. Vì vậy, bộ đệm kỹ thuật số là một bộ “không đảo” và do đó sẽ cho chúng ta những biểu thức Boolean của: Q = A .

Sau đó, chúng ta có thể xác định hoạt động hợp lý của một Cổng đệm buffer đầu vào duy nhất là:

“Q đúng, chỉ khi A đúng”

Nói cách khác, trạng thái đầu ra ( Q ) của bộ đệm chỉ đúng (logic “1”) khi đầu vào A của nó là đúng, nếu không đầu ra của nó là sai (logic “0”).

Cổng đệm buffer đầu vào duy nhất

| Biểu tượng | Bảng sự thật | |

Bộ đệm kỹ thuật số |

A | Q |

| 0 | 0 | |

| 1 | 1 | |

| Biểu thức Boolean Q = A | Đọc như: A cho Q | |

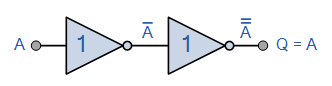

Bộ đệm kỹ thuật số cũng có thể được thực hiện bằng cách kết nối hai cổng NOT với nhau như hình dưới đây. Đầu tiên sẽ “đảo” tín hiệu đầu vào A và tín hiệu thứ hai sẽ “đảo ” tín hiệu trở lại mức ban đầu, thực hiện đảo kép đầu vào.

Đảo kép sử dụng cổng NOT – Cổng đệm buffer

Bạn có thể đang nghĩ, mục đích của Digital Buffer là gì nếu nó không đảo hoặc thay đổi tín hiệu đầu vào của nó theo bất kỳ cách nào hoặc đưa ra bất kỳ quyết định hoặc hoạt động logic nào như cổng AND hoặc OR . Nhưng Cổng đệm buffer không đảo có nhiều ứng dụng trong điện tử kỹ thuật số với một trong những ưu điểm chính của nó là nó cung cấp khả năng khuếch đại kỹ thuật số.

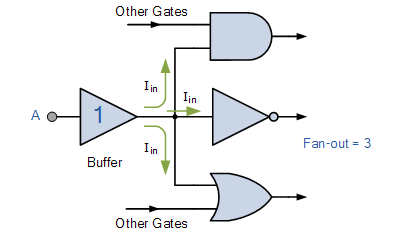

Cổng đệm buffer có thể được sử dụng để cách ly các cổng hoặc tầng mạch khác với nhau ngăn cản trở kháng của một mạch ảnh hưởng đến trở kháng của mạch khác. Bộ đệm kỹ thuật số cũng có thể được sử dụng để điều khiển tải dòng điện cao như công tắc bóng bán dẫn vì khả năng truyền động đầu ra của chúng thường cao hơn nhiều so với yêu cầu tín hiệu đầu vào của chúng. Nói cách khác, bộ đệm có thể được sử dụng để khuếch đại công suất của tín hiệu kỹ thuật số vì chúng có khả năng “fan-out” cao.

Fan-out : Trong điện tử kỹ thuật số, fan-out là số lượng đầu vào cổng được điều khiển bởi đầu ra của một cổng logic đơn khác. Trong hầu hết các thiết kế, cổng logic được kết nối để tạo thành các mạch phức tạp hơn.

Ví dụ về fan-out Cổng đệm buffer

Các Fan-out tham số của một bộ đệm (hoặc bất kỳ vi mạch kỹ thuật số) là khả năng điều khiển đầu ra hoặc khả năng dòng điện đầu ra của một cổng logic để khuếch đại công suất lớn hơn của tín hiệu đầu vào. Có thể cần kết nối nhiều hơn chỉ một cổng logic với đầu ra của một cổng khác hoặc chuyển tải dòng điện cao như đèn LED, khi đó Bộ đệm sẽ cho phép chúng ta làm điều đó.

Nói chung đầu ra của cổng logic thường được kết nối với đầu vào của các cổng khác. Mỗi đầu vào yêu cầu một lượng dòng điện nhất định từ đầu ra cổng để thay đổi trạng thái, do đó mỗi kết nối cổng bổ sung sẽ bổ sung thêm tải của cổng. Vì vậy, fan-out là số tải song song có thể được điều khiển đồng thời bởi một Cổng đệm buffer của cổng logic. Hoạt động như một nguồn dòng, bộ đệm có thể có fan-out cao lên đến 20 cổng của cùng một họ logic.

Nếu Cổng đệm buffer có xếp hạng fan-out cao (nguồn dòng) thì nó cũng phải có xếp hạng “fan-in” cao (bộ đệm dòng). Tuy nhiên, độ trễ lan truyền của cổng giảm nhanh chóng do chức năng của fan-in, vì vậy cần tránh các cổng có fan-in lớn hơn 4.

Sau đó, có một giới hạn về số lượng đầu vào và đầu ra có thể được kết nối với nhau và trong các ứng dụng mà chúng ta cần tách các cổng khỏi nhau, chúng ta có thể sử dụng Cổng đệm ba trạng thái hoặc trình điều khiển đầu ra ba trạng thái .

“Cổng đệm ba trạng thái” – Cổng đệm buffer

Cũng như cổng đếm buffer tiêu chuẩn đã thấy ở trên, có một loại mạch đệm kỹ thuật số khác mà đầu ra của nó có thể được ngắt kết nối “điện tử” khỏi mạch đầu ra của nó khi được yêu cầu. Loại bộ đệm này được gọi là cổng đệm ba trạng thái .

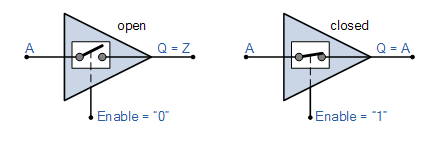

Một cổng đệm 3 trạng thái có thể được coi như một đầu vào điều khiển công tắc với đầu ra có thể “ON” hoặc “OFF” bằng cách điều khiển từ bên ngoài “Enable” ( EN ) tín hiệu đầu vào. Tín hiệu điều khiển này có thể là tín hiệu logic “0” hoặc tín hiệu loại logic “1” dẫn đến Bộ đệm ba trạng thái ở một trạng thái cho phép đầu ra của nó hoạt động bình thường tạo ra đầu ra yêu cầu hoặc ở trạng thái khác đầu ra của nó bị chặn hoặc ngắt kết nối.

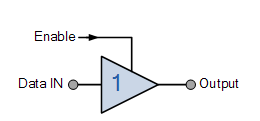

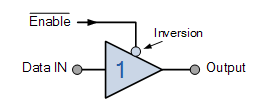

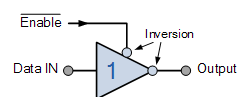

Bộ đệm ba trạng thái yêu cầu hai đầu vào. Một là đầu vào dữ liệu và một là đầu vào kích hoạt hoặc điều khiển như được hiển thị.

Công tắc đệm ba trạng thái tương đương

Khi được kích hoạt ở trạng thái thứ ba, nó sẽ vô hiệu hóa hoặc “TẮT” đầu ra của nó tạo ra tình trạng hở mạch không ở mức logic “CAO” hoặc “THẤP”, mà thay vào đó là trạng thái đầu ra có trở kháng rất cao, Hi-Z . Sau đó, loại thiết bị này có hai đầu vào trạng thái logic, “0” hoặc “1” nhưng có thể tạo ra ba trạng thái đầu ra khác nhau, “0”, “1” hoặc “ Hi-Z ”, đó là lý do tại sao nó được gọi là “Tri” hoặc cổng “3 trạng thái”.

Lưu ý rằng trạng thái thứ ba này KHÔNG bằng mức logic “0” hoặc “1”, nhưng là trạng thái trở kháng cao, trong đó đầu ra bộ đệm bị ngắt kết nối điện khỏi phần còn lại của mạch. Kết quả là, không có dòng điện nào từ nguồn cung cấp.

Có bốn loại Bộ đệm ba trạng thái khác nhau , một bộ có đầu ra được bật hoặc tắt bởi tín hiệu điều khiển “ Active-HIGH ” tạo ra đầu ra đảo hoặc không đảo và một bộ khác có đầu ra bộ đệm được điều khiển bởi “ Active-LOW ”tạo ra đầu ra đảo hoặc không đảo như hình dưới đây.

Bộ đệm ba trạng thái “CAO” tích cực – Cổng đệm buffer

| Biểu tượng | Bảng sự thật | ||

Bộ đệm ba trạng thái |

Enable | IN | OUT |

| 0 | 0 | Hi-Z | |

| 0 | 1 | Hi-Z | |

| 1 | 0 | 0 | |

| 1 | 1 | 1 | |

Active-HIGHT Tri-state Buffer như 74LS241 đệm bát phân, được kích hoạt khi một mức logic “1” được áp dụng để “kích hoạt” dòng điều khiển của nó và các dữ liệu đi qua từ đầu vào của nó đến đầu ra. Khi dòng điều khiển kích hoạt ở mức logic “0”, đầu ra bộ đệm bị vô hiệu hóa và điều kiện trở kháng cao, Hi-Z xuất hiện trên đầu ra.

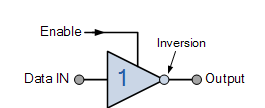

Bộ đệm ba trạng thái Active-HIGHT cũng có thể có đầu ra đảo cũng như trạng thái trở kháng cao của nó tạo ra bộ đệm đảo ba trạng thái cao hoạt động như được minh họa.

Bộ đệm ba trạng thái đảo Active-HIGHT

| Biểu tượng | Bảng sự thật | ||

Bộ đệm đảo ba trạng thái |

Enable | IN | OUT |

| 0 | 0 | Hi-Z | |

| 0 | 1 | Hi-Z | |

| 1 | 0 | 1 | |

| 1 | 1 | 0 | |

Đầu ra của Bộ đệm ba trạng thái đảo Active-HIGHT, chẳng hạn như bộ đệm bát phân 74LS240, được kích hoạt khi mức logic “1” được áp dụng cho dòng điều khiển “enable” của nó. Dữ liệu ở đầu vào được chuyển qua đầu ra nhưng bị đảo tạo ra phần bổ sung của đầu vào. Khi dòng kích hoạt ở mức THẤP ở mức logic “0”, đầu ra bộ đệm bị tắt và ở điều kiện trở kháng cao, Hi-Z .

Hai bộ đệm ba trạng thái giống nhau cũng có thể được thực hiện với đầu vào kích hoạt hoạt động ở mức thấp như được minh họa.

Bộ đệm ba trạng thái Active-LOW

| Biểu tượng | Bảng sự thật | ||

Bộ đệm ba trạng thái |

Enable | IN | OUT |

| 0 | 0 | 0 | |

| 0 | 1 | 1 | |

| 1 | 0 | Hi-Z | |

| 1 | 1 | Hi-Z | |

Bộ đệm ba trạng thái Active-LOW đối lập với ở trên, và được kích hoạt khi một mức logic “0” được áp dụng “cho phép ” dòng điều khiển. Dữ liệu đi qua từ đầu vào đến đầu ra của nó. Khi dòng điều khiển cho phép ở mức logic “1”, đầu ra bộ đệm bị vô hiệu hóa và điều kiện trở kháng cao, Hi-Z xuất hiện trên đầu ra.

Bộ đệm ba trạng thái đảo Active-LOW

| Biểu tượng | Bảng sự thật | ||

Bộ đệm Đảo ba trạng thái |

Enable | IN | OUT |

| 0 | 0 | 1 | |

| 0 | 1 | 0 | |

| 1 | 0 | Hi-Z | |

| 1 | 1 | Hi-Z | |

Bộ đệm ba trạng thái đảo Active-LOW đầu của nó được kích hoạt hoặc vô hiệu hóa khi mức logic “0” được áp dụng “cho phép ” dòng điều khiển. Khi một bộ đệm được kích hoạt bởi logic “0”, đầu ra là phần bổ sung của đầu vào của nó. Khi dòng điều khiển cho phép ở mức logic “1”, đầu ra bộ đệm bị vô hiệu hóa và điều kiện trở kháng cao, Hi-Z xuất hiện trên đầu ra.

Điều khiển bộ đệm ba trạng thái

Chúng ta đã thấy ở trên rằng một bộ đệm có thể cung cấp điện áp hoặc khuếch đại dòng điện trong mạch kỹ thuật số và nó cũng có thể được sử dụng để đảo tín hiệu đầu vào. Chúng tôi cũng đã thấy rằng các bộ đệm kỹ thuật số có sẵn ở dạng ba trạng thái cho phép đầu ra được đóng ngắt một cách hiệu quả tạo ra trạng thái trở kháng cao (Hi-Z) tương đương với một mạch hở.

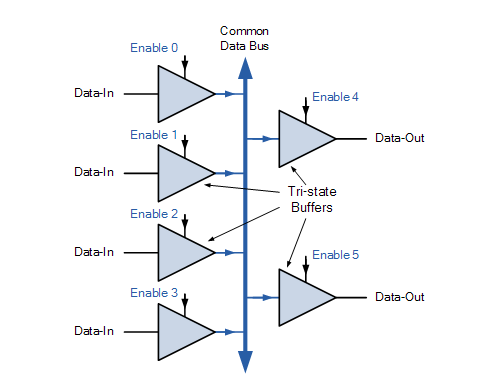

Bộ đệm ba trạng thái được sử dụng trong nhiều mạch điện tử và vi xử lý vì chúng cho phép nhiều thiết bị logic được kết nối với cùng một dây hoặc bus mà không làm hỏng hoặc mất dữ liệu. Ví dụ: giả sử chúng ta có một đường dữ liệu hoặc bus dữ liệu với một số bộ nhớ, thiết bị ngoại vi, I / O hoặc CPU được kết nối với nó. Mỗi thiết bị này có khả năng gửi hoặc nhận dữ liệu cho nhau trên bus dữ liệu duy nhất này đồng thời tạo ra cái được gọi là tranh chấp.

Xung đột xảy ra khi nhiều thiết bị được kết nối với nhau vì một số muốn tăng đầu ra của chúng ở mức cao và một số ở mức thấp. Nếu các thiết bị này bắt đầu gửi hoặc nhận dữ liệu cùng một lúc, có thể xảy ra ngắn mạch khi một thiết bị xuất ra bus mức logic “1”, điện áp nguồn, trong khi thiết bị khác được đặt ở mức logic “0” hoặc nối đất, dẫn đến tình trạng đoản mạch và có thể làm hỏng thiết bị cũng như mất dữ liệu.

Thông tin kỹ thuật số được gửi qua các bus dữ liệu này hoặc đường dữ liệu hi-speed nối tiếp, từng bit một hoặc có thể lên đến tám (hoặc nhiều) dây với nhau ở dạng song song chẳng hạn như trong bus dữ liệu của bộ vi xử lý cho phép nhiều bộ đệm ba trạng thái được kết nối với cùng một đường cao tốc dữ liệu mà không làm hỏng hoặc mất dữ liệu như hình minh họa.

Điều khiển bus dữ liệu bộ đệm ba trạng thái

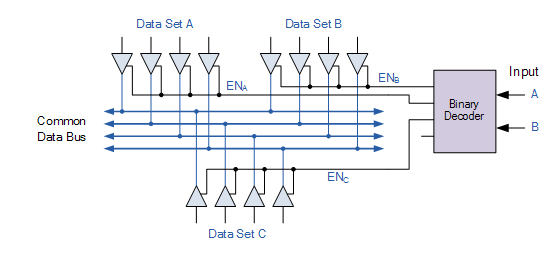

Bộ đệm ba trạng thái có thể được sử dụng để cách ly các thiết bị và mạch khỏi bus dữ liệu và với nhau. Nếu đầu ra của một số Bộ đệm ba trạng thái được kết nối điện với nhau Bộ giải mã được sử dụng để cho phép chỉ một bộ Bộ đệm ba trạng thái hoạt động tại một thời điểm bất kỳ trong khi các thiết bị khác ở trạng thái trở kháng cao. Dưới đây là ví dụ về Bộ đệm ba trạng thái được kết nối với bus dữ liệu 4 dây.

Điều khiển bộ đệm ba trạng thái

Ví dụ cơ bản này cho thấy cách một bộ giải mã nhị phân có thể được sử dụng để điều khiển một số bộ đệm ba trạng thái riêng lẻ hoặc cùng nhau trong tập dữ liệu. Bộ giải mã chọn đầu ra thích hợp tương ứng với đầu vào nhị phân của nó, chỉ cho phép một tập dữ liệu chuyển trạng thái đầu ra logic “1” hoặc logic “0” lên bus. Tại thời điểm này, tất cả các đầu ra ba trạng thái khác được kết nối với cùng một đường bus đều bị vô hiệu hóa do được đặt ở trạng thái Hi-Z trở kháng cao của chúng .

Sau đó, dữ liệu từ bộ dữ liệu “A” chỉ có thể được chuyển sang xe buýt thông thường khi một tín hiệu CAO hoạt động được áp dụng cho các bộ đệm tri-state qua dòng Enable, EN Một . Tại tất cả các thời điểm khác, nó thể hiện tình trạng trở kháng cao được cách ly khỏi bus dữ liệu.

Tương tự như vậy, bộ dữ liệu “B” chỉ đi dữ liệu vào xe buýt khi một phép tín hiệu được áp dụng thông qua EN B . Một ví dụ điển hình về bộ đệm ba trạng thái được kết nối với nhau để điều khiển tập dữ liệu là Bộ đệm bát phân TTL 74244.

Cũng có thể kết nối Bộ đệm ba trạng thái “ngược lại” để tạo ra cái được gọi là mạch Bộ đệm hai hướng với một “bộ đệm hoạt động-cao” được kết nối song song nhưng ngược lại với một “bộ đệm hoạt động-thấp” .

Ở đây, đầu vào điều khiển “enable” hoạt động giống như một tín hiệu điều khiển định hướng khiến dữ liệu vừa được đọc “từ” vừa được truyền “tới” cùng một dây bus dữ liệu. Trong loại ứng dụng này, có thể sử dụng bộ đệm ba trạng thái với khả năng chuyển đổi hai chiều như TTL 74245.

Chúng ta đã thấy rằng bộ đệm 3 trạng thái là một thiết bị không đảo , chỉ cung cấp đầu ra (giống như đầu vào của nó) khi đầu vào cho chân Enable, ( EN ) là CAO nếu không đầu ra của bộ đệm sẽ đi vào trở kháng cao, trạng thái ( Hi-Z ). Đầu ra ba trạng thái được sử dụng trong nhiều mạch tích hợp và hệ thống kỹ thuật số chứ không chỉ trong bộ đệm tristate kỹ thuật số.

Cả bộ đệm kỹ thuật số và bộ đệm ba trạng thái đều có thể được sử dụng để cung cấp điện áp hoặc khuếch đại dòng điện dẫn đến các tải cao như rơ le, đèn hoặc bóng bán dẫn điện hơn so với các cổng logic thông thường. Nhưng một bộ đệm cũng có thể được sử dụng để cách ly điện giữa hai hoặc nhiều mạch.

Chúng tôi đã thấy rằng một bus dữ liệu có thể được tạo ra nếu một số thiết bị tristate được kết nối với nhau và miễn là chỉ một thiết bị được chọn cùng một lúc thì không có vấn đề gì. Các bus ba trạng thái cho phép một số thiết bị kỹ thuật số nhập và xuất dữ liệu trên cùng một bus dữ liệu bằng cách sử dụng các tín hiệu I / O và giải mã địa chỉ.

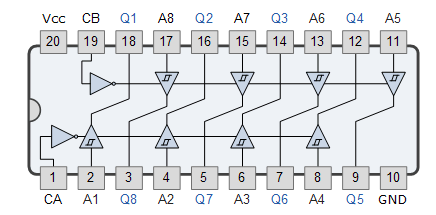

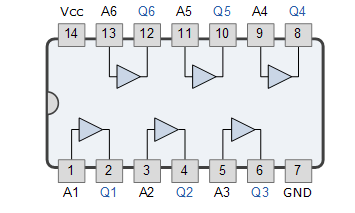

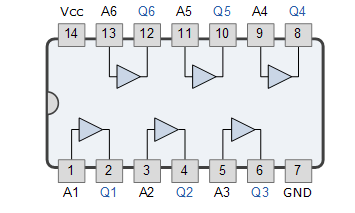

Bộ đệm ba trạng thái có sẵn ở dạng tích hợp dưới dạng bộ đệm / trình điều khiển bốn, sáu hoặc bát phân ở cả hai dạng đơn hướng và hai hướng, phổ biến hơn là TTL 74240, TTL 74244 và TTL 74245 như được minh họa.

Bộ đệm kỹ thuật số và IC đệm ba trạng thái thường có sẵn bao gồm:

Bộ đệm kỹ thuật số logic TTL

- 74LS07 Bộ đệm không đảo Hex

- 74LS17 Bộ đệm Hex / Trình điều khiển

- 74LS244 Bộ đệm bát phân / Trình điều khiển dòng

- 74LS245 Bộ đệm hai hướng bát phân

Bộ đệm kỹ thuật số logic CMOS

- CD4050 Bộ đệm không đảo Hex

- CD4503 Bộ đệm ba trạng thái Hex

- HEF40244 Bộ đệm bát phân ba trạng thái

Bộ đệm kỹ thuật số 74LS07

74LS244 Bộ đệm ba trạng thái bát phân